Memory Mapping In 8085

If you're looking for memory mapping in 8085 images information related to the memory mapping in 8085 keyword, you have pay a visit to the ideal site. Our site frequently provides you with suggestions for viewing the highest quality video and image content, please kindly hunt and locate more enlightening video content and graphics that match your interests.

Memory Mapping In 8085

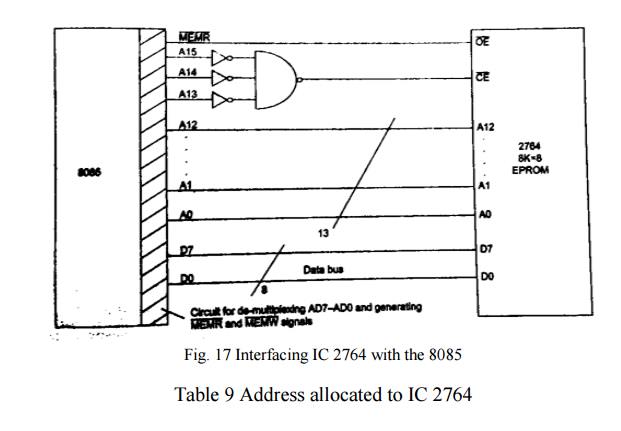

My question is, why is rom always mapped to a lower region of memory map in the 8085 microprocessor? The memory address space of the 8085 takes values from 0000h to ffffh. We can connect the rd’ or wr’ lines from the microprocessor to the coprresponding rd’ and wr’ pins of the memory ic.

The output device can be connected. Thus, we can say that 8085 can support a memory chip of size up to 64 kb. It starts program execution with the next address field.

The flow of an instruction cycle in 8085 architecture :

8085 memory organization 8085 has 16 address lines, so it can address up to 64kb of memory. Memory and i/o have separate address space. Port mapped i/o uses a separate, dedicated address space and is accessed via a dedicated set of microprocessor instructions. Data is transferred only between the accumulator and i.o port.

If you find this site convienient , please support us by sharing this posts to your favorite social media accounts like Facebook, Instagram and so on or you can also save this blog page with the title memory mapping in 8085 by using Ctrl + D for devices a laptop with a Windows operating system or Command + D for laptops with an Apple operating system. If you use a smartphone, you can also use the drawer menu of the browser you are using. Whether it's a Windows, Mac, iOS or Android operating system, you will still be able to save this website.